«پایان بیانیه مطبوعاتی»

«پایان بیانیه مطبوعاتی»

اسکات هاتون، مدیر کل Interface IP در Rambus، گفت: «پیشرفت سریع هوش مصنوعی/ML و حجمهای کاری پرمصرف داده، منجر به تکامل مداوم معماریهای مرکز داده میشود که به سطوح بالاتری از عملکرد نیاز دارند. زیرسیستم رابط Rambus PCIe 6.0 از الزامات عملکرد مراکز داده نسل بعدی با تأخیر، قدرت، منطقه و امنیت برتر پشتیبانی می کند.

Shane Rau، معاون پژوهشی بخش نیمه هادی های محاسباتی IDC گفت: «PCIe در مرکز داده همه جا حاضر است و CXL اهمیت فزاینده ای پیدا می کند زیرا شرکت ها به دنبال افزایش سرعت و پهنای باند برای پشتیبانی از سطوح بالاتر عملکرد در برنامه های نسل بعدی هستند. از آنجایی که تعداد فزایندهای از شرکتهای تولید تراشه برای پشتیبانی از معماریهای جدید مرکز داده ظهور میکنند، دسترسی به راهحلهای IP رابط با کارایی بالا کلیدی برای فعال کردن اکوسیستم خواهد بود.

نکات برجسته:

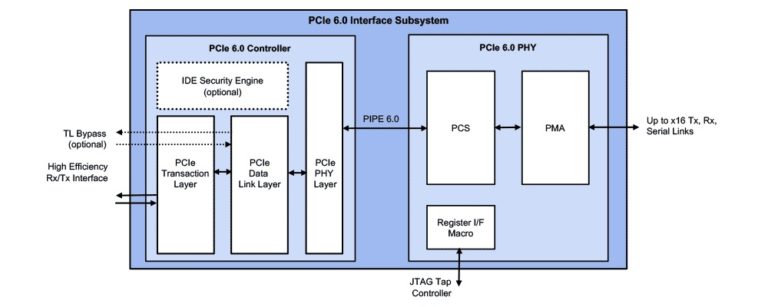

زیرسیستم واسط Rambus PCIe 6.0 نرخ داده تا 64 گیگاترانسفر در ثانیه (GT/s) را ارائه می دهد و به طور کامل برای پاسخگویی به نیازهای معماری های محاسباتی ناهمگن پیشرفته بهینه شده است. در داخل زیرسیستم، کنترلر PCIe دارای یک موتور یکپارچگی و رمزگذاری داده (IDE) است که برای محافظت از پیوندهای PCIe و داده های ارزشمند منتقل شده روی آنها اختصاص داده شده است. در سمت PHY، پشتیبانی کامل از CXL 3.0 برای فعال کردن راهحلهای سطح تراشه برای اشتراکگذاری، گسترش و ادغام حافظه منسجم با حافظه پنهان در دسترس است.